You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

Staff Posts

Recent threadmarks

sharing files

Important Posts

Recent threadmarks

FirmwaresWell, since some guys are still reversing the firmware, and PIO has been completely spoiled by flynn, here is the (v2.6) PIO code with my comments. actually, that is the heart of the firmware, like the FPGA part of hwfly.

This reveals like half of inventions totally made.

This reveals like half of inventions totally made.

Code:

.program sd_clk

.side_set 1

.wrap_target

; open-drain RST switcher to keep the CPU in reset state

set pindirs, 0 side 1 ; side-set push-pull eMMC clocker (2mA limit is set to prevent damage)

irq clear 0 side 0 ; rising edge sync made with IRQs

set pindirs, 1 side 1

irq clear 0 side 0

.wrap

.program out_cmd_or_dat

.wrap_target

out x, 16 ; first word is the write size

irq wait 0 [1] ; the next cmd will go on falling edge

send_loop:

out pindirs, 1 ; use open-drain just in case, to prevent 3.3v damage

jmp x-- send_loop

irq clear 1 ; unblock the reader

out NULL, 32 ; clear the osr

.wrap

.program in_cmd_or_dat

.wrap_target

out x, 32 ;get read size

irq wait 1 ;wait for cmd send to finish

irq wait 0 ;sync with clock, next cmd will go at rising edge

data_wait:

jmp pin, data_wait [1] ; sync pin wait with rising edge

read_loop:

in pins, 1 ; here we always at the rising edge

jmp x-- read_loop

push

.wrap

.program glitch_sniff_cmd

.wrap_target

next_loop:

mov x, osr ; mmc command pre-loaded bits count (48 - 1 - 1)

wait_for_start_bit:

wait 0 pin, 31

wait 1 pin, 31

jmp pin wait_for_start_bit ; wait for cmd start bit on the rising edge

wait 0 pin, 31

; waits separated by only 1 instruction, should be able to catch 50 MHz

in NULL, 1

read_loop:

wait 1 pin, 31

in pins, 1 ; command sniffer

wait 0 pin, 31

jmp x-- read_loop

irq clear 2 ; 'some cmd has passed' trigger

mov x, isr ; save the last 16 bit of command

push ; send the rest 16 bits of data

jmp x != y, next_loop ; compare the glitch pattern (0x1351, read block + crc)

irq clear 0 ; 'glitch pattern' trigger

.wrap

.program glitch_dat_waiter

.wrap_target

mov x, y ; data length pre-loaded counter (512 + 16 - 1)

wait_for_start_bit:

wait 0 pin, 30

wait 1 pin, 30

jmp pin wait_for_start_bit ; wait for dat start bit of the rising edge

wait 0 pin, 30

skip_loop_dat:

wait 1 pin, 30

;in pins, 1 ; data sniffer (not needed anymore, removed to fit 50mhz code)

wait 0 pin, 30

jmp x-- skip_loop_dat ; skip the required data ticks

irq clear 1 ; 'data transfer done' trigger

.wrap

.program glitch_trigger

.side_set 1

.wrap_target

out x, 32 side 0 ; receive wait timing

out y, 32 side 0 ; receive pulse timing

irq wait 0 side 0 ; wait for read 13

irq wait 1 side 0 ; wait for data transfer

irq wait 2 side 0 ; wait for status request (should be NOPped for Mariko)

irq wait 2 side 0 ; wait for status reply (should be NOPped for Mariko)

wait_for_timing:

jmp x--, wait_for_timing side 0

glitch_en:

jmp y--, glitch_en side 1

.wrap- Joined

- Sep 2, 2020

- Messages

- 1,274

- Trophies

- 0

- Age

- 39

- Location

- TORONTO

- Website

- form.jotform.com

- XP

- 2,204

- Country

To ebay!thanks thanks :-)

so who is already looking for there broken ps4 controllers

Well, since some guys are still reversing the firmware, and PIO has been completely spoiled by flynn, here is the (v2.6) PIO code with my comments. actually, that is the heart of the firmware, like the FPGA part of hwfly.

This reveals like half of inventions totally made.

Code:.program sd_clk .side_set 1 .wrap_target ; open-drain RST switcher to keep the CPU in reset state set pindirs, 0 side 1 ; side-set push-pull eMMC clocker (2mA limit is set to prevent damage) irq clear 0 side 0 ; rising edge sync made with IRQs set pindirs, 1 side 1 irq clear 0 side 0 .wrap .program out_cmd_or_dat .wrap_target out x, 16 ; first word is the write size irq wait 0 [1] ; the next cmd will go on falling edge send_loop: out pindirs, 1 ; use open-drain just in case, to prevent 3.3v damage jmp x-- send_loop irq clear 1 ; unblock the reader out NULL, 32 ; clear the osr .wrap .program in_cmd_or_dat .wrap_target out x, 32 ;get read size irq wait 1 ;wait for cmd send to finish irq wait 0 ;sync with clock, next cmd will go at rising edge data_wait: jmp pin, data_wait [1] ; sync pin wait with rising edge read_loop: in pins, 1 ; here we always at the rising edge jmp x-- read_loop push .wrap .program glitch_sniff_cmd .wrap_target next_loop: mov x, osr ; mmc command pre-loaded bits count (48 - 1 - 1) wait_for_start_bit: wait 0 pin, 31 wait 1 pin, 31 jmp pin wait_for_start_bit ; wait for cmd start bit on the rising edge wait 0 pin, 31 ; waits separated by only 1 instruction, should be able to catch 50 MHz in NULL, 1 read_loop: wait 1 pin, 31 in pins, 1 ; command sniffer wait 0 pin, 31 jmp x-- read_loop irq clear 2 ; 'some cmd has passed' trigger mov x, isr ; save the last 16 bit of command push ; send the rest 16 bits of data jmp x != y, next_loop ; compare the glitch pattern (0x1351, read block + crc) irq clear 0 ; 'glitch pattern' trigger .wrap .program glitch_dat_waiter .wrap_target mov x, y ; data length pre-loaded counter (512 + 16 - 1) wait_for_start_bit: wait 0 pin, 30 wait 1 pin, 30 jmp pin wait_for_start_bit ; wait for dat start bit of the rising edge wait 0 pin, 30 skip_loop_dat: wait 1 pin, 30 ;in pins, 1 ; data sniffer (not needed anymore, removed to fit 50mhz code) wait 0 pin, 30 jmp x-- skip_loop_dat ; skip the required data ticks irq clear 1 ; 'data transfer done' trigger .wrap .program glitch_trigger .side_set 1 .wrap_target out x, 32 side 0 ; receive wait timing out y, 32 side 0 ; receive pulse timing irq wait 0 side 0 ; wait for read 13 irq wait 1 side 0 ; wait for data transfer irq wait 2 side 0 ; wait for status request (should be NOPped for Mariko) irq wait 2 side 0 ; wait for status reply (should be NOPped for Mariko) wait_for_timing: jmp x--, wait_for_timing side 0 glitch_en: jmp y--, glitch_en side 1 .wrap

2.6? New fw?

Lot of respects for you guys. Huge work here, congrats.

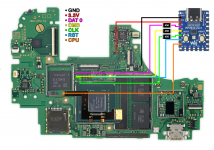

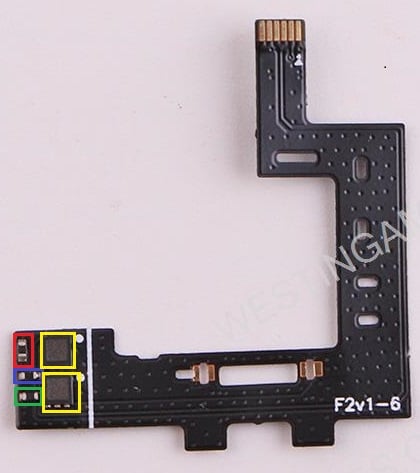

Can someone please give me the values of those resistor, red, blue, green, and those two mosfets in yellow ?

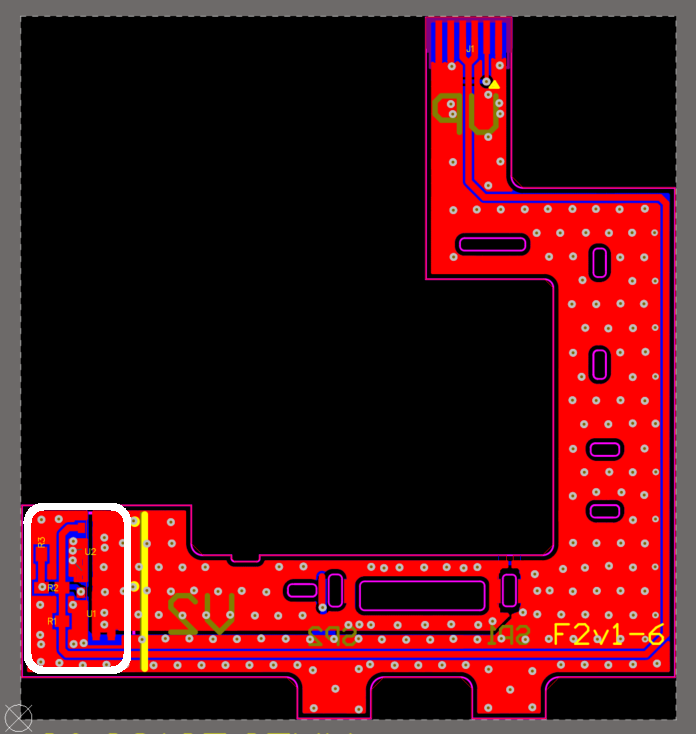

Also do you know with which software can we open leaked HWFly leaks schematics/ board files ? I tried Eagle/Kicad they are not working. Altium works but layout of pcb seems broken (see where the mosfet emplacement should be in white):

Thanks

Can someone please give me the values of those resistor, red, blue, green, and those two mosfets in yellow ?

Also do you know with which software can we open leaked HWFly leaks schematics/ board files ? I tried Eagle/Kicad they are not working. Altium works but layout of pcb seems broken (see where the mosfet emplacement should be in white):

Thanks

Oh boy, here we go (again)!!Well, since some guys are still reversing the firmware, and PIO has been completely spoiled by flynn, here is the (v2.6) PIO code with my comments. actually, that is the heart of the firmware, like the FPGA part of hwfly.

This reveals like half of inventions totally made.

Code:.program sd_clk .side_set 1 .wrap_target ; open-drain RST switcher to keep the CPU in reset state set pindirs, 0 side 1 ; side-set push-pull eMMC clocker (2mA limit is set to prevent damage) irq clear 0 side 0 ; rising edge sync made with IRQs set pindirs, 1 side 1 irq clear 0 side 0 .wrap .program out_cmd_or_dat .wrap_target out x, 16 ; first word is the write size irq wait 0 [1] ; the next cmd will go on falling edge send_loop: out pindirs, 1 ; use open-drain just in case, to prevent 3.3v damage jmp x-- send_loop irq clear 1 ; unblock the reader out NULL, 32 ; clear the osr .wrap .program in_cmd_or_dat .wrap_target out x, 32 ;get read size irq wait 1 ;wait for cmd send to finish irq wait 0 ;sync with clock, next cmd will go at rising edge data_wait: jmp pin, data_wait [1] ; sync pin wait with rising edge read_loop: in pins, 1 ; here we always at the rising edge jmp x-- read_loop push .wrap .program glitch_sniff_cmd .wrap_target next_loop: mov x, osr ; mmc command pre-loaded bits count (48 - 1 - 1) wait_for_start_bit: wait 0 pin, 31 wait 1 pin, 31 jmp pin wait_for_start_bit ; wait for cmd start bit on the rising edge wait 0 pin, 31 ; waits separated by only 1 instruction, should be able to catch 50 MHz in NULL, 1 read_loop: wait 1 pin, 31 in pins, 1 ; command sniffer wait 0 pin, 31 jmp x-- read_loop irq clear 2 ; 'some cmd has passed' trigger mov x, isr ; save the last 16 bit of command push ; send the rest 16 bits of data jmp x != y, next_loop ; compare the glitch pattern (0x1351, read block + crc) irq clear 0 ; 'glitch pattern' trigger .wrap .program glitch_dat_waiter .wrap_target mov x, y ; data length pre-loaded counter (512 + 16 - 1) wait_for_start_bit: wait 0 pin, 30 wait 1 pin, 30 jmp pin wait_for_start_bit ; wait for dat start bit of the rising edge wait 0 pin, 30 skip_loop_dat: wait 1 pin, 30 ;in pins, 1 ; data sniffer (not needed anymore, removed to fit 50mhz code) wait 0 pin, 30 jmp x-- skip_loop_dat ; skip the required data ticks irq clear 1 ; 'data transfer done' trigger .wrap .program glitch_trigger .side_set 1 .wrap_target out x, 32 side 0 ; receive wait timing out y, 32 side 0 ; receive pulse timing irq wait 0 side 0 ; wait for read 13 irq wait 1 side 0 ; wait for data transfer irq wait 2 side 0 ; wait for status request (should be NOPped for Mariko) irq wait 2 side 0 ; wait for status reply (should be NOPped for Mariko) wait_for_timing: jmp x--, wait_for_timing side 0 glitch_en: jmp y--, glitch_en side 1 .wrap

Thank you @rehius

ThanksThe MOSFETs are already present in the cable, you should be just good to go with it only.

The resistors are necessary for filtering signal interference and for booting into SYSMMC, more info just few pages ago.

the PIO has been updated since v2.5, so yes, this one should be in the next fw2.6? New fw?

what changes or improvements await us?the PIO has been updated since v2.5, so yes, this one should be in the next fw

mainly, software update supportwhat changes or improvements await us?

any idea what sort of time frame to release so I can update my thread?mainly, software update support

Why not give @rehius access to update it? So it's consolidated to one thread?any idea what sort of time frame to release so I can update my thread?

no idea, there are three more things to make & test for itany idea what sort of time frame to release so I can update my thread?

Isn't the difference just the usb port?does this tiny friend work?

Latest firmware here

ChangeLog:

v2.0 + Active MMC communication

v2.1 + Toshiba support

v2.2 + Fix Toshiba boot fail

v2.3 + SanDisk support

v2.4 + Faster Toshiba boot

v2.5 + fix OFW boot

must be RED after USB write. if you see green, set "RGB mode" jumper

WHITE = eMMC write

BLUE = glitch

PURPLE = eMMC boot failure, check CMD / CLK

YELLOW = eMMC write failure, check D0 / unsupported eMMC

CYAN = no reaction to glitch, check mosfet wire

GREEN = success

Q: What is supported?

A: Erista (v1), Mariko (v2, Lite, OLED)

Q: eMMC types support?

A: Tested on Hynix, Samsung, Toshiba, SanDisk

Q: GREEN, but instant reset

A: Check your soldering, clean flux. If does not help = add 20K-30K to RST

Q: Do I really need 47 Ohm resistors?

A: You can skip them, however in this case you will have to use emuMMC due to the line interference, sysNAND would not boot.

Q: Does the firmware has learning? How to reset statistics

A: Short pin 0 to either 1 or GND during start for chip reset. The statistics is collected each boot. The more you start it - the better it boots.

Q: open source?

A: no

Q: why you made it?

A: to prove it possible!

Q: run Atmosphere?

A: no piracy

By using the Atmosphere unlock tool you agree to use it for homebrew only.

Way 1 (USB): flash the unlock.uf2 into chip by USB

Way 2 (no USB): run picofly_tb from Hekate, need unlock.bin on the SD card

Boot into Full Stock and perform a full system reset.

Hi, sorry for the inconvenience, but is there a diagram to install the chip with the hwfly Flex cables in the V2 and Oled? I saw that there is a diagram for the Lite that uses the third pin of the Flex cable to take it to the "cpu" pinout on the rp2040, I don't know if this also applies to the V2 and the Oled

Attachments

Yes, resistors still needed thodoes this tiny friend work?

Similar threads

- Replies

- 3

- Views

- 932

- Replies

- 42

- Views

- 6K

- Replies

- 5

- Views

- 1K

- Replies

- 6

- Views

- 2K

- Replies

- 8

- Views

- 2K

Site & Scene News

New Hot Discussed

-

-

26K views

Atmosphere CFW for Switch updated to pre-release version 1.7.0, adds support for firmware 18.0.0

After a couple days of Nintendo releasing their 18.0.0 firmware update, @SciresM releases a brand new update to his Atmosphere NX custom firmware for the Nintendo...by ShadowOne333 107 -

21K views

Wii U and 3DS online services shutting down today, but Pretendo is here to save the day

Today, April 8th, 2024, at 4PM PT, marks the day in which Nintendo permanently ends support for both the 3DS and the Wii U online services, which include co-op play...by ShadowOne333 179 -

17K views

GBAtemp Exclusive Introducing tempBOT AI - your new virtual GBAtemp companion and aide (April Fools)

Hello, GBAtemp members! After a prolonged absence, I am delighted to announce my return and upgraded form to you today... Introducing tempBOT AI 🤖 As the embodiment... -

14K views

The first retro emulator hits Apple's App Store, but you should probably avoid it

With Apple having recently updated their guidelines for the App Store, iOS users have been left to speculate on specific wording and whether retro emulators as we... -

13K views

MisterFPGA has been updated to include an official release for its Nintendo 64 core

The highly popular and accurate FPGA hardware, MisterFGPA, has received today a brand new update with a long-awaited feature, or rather, a new core for hardcore...by ShadowOne333 54 -

13K views

Delta emulator now available on the App Store for iOS

The time has finally come, and after many, many years (if not decades) of Apple users having to side load emulator apps into their iOS devices through unofficial...by ShadowOne333 96 -

12K views

Nintendo Switch firmware update 18.0.1 has been released

A new Nintendo Switch firmware update is here. System software version 18.0.1 has been released. This update offers the typical stability features as all other... -

11K views

"TMNT: The Hyperstone Heist" for the SEGA Genesis / Mega Drive gets a brand new DX romhack with new features

The romhacking community is always a source for new ways to play retro games, from completely new levels or stages, characters, quality of life improvements, to flat...by ShadowOne333 36 -

10K views

Anbernic announces RG35XX 2024 Edition retro handheld

Retro handheld manufacturer Anbernic is releasing a refreshed model of its RG35XX handheld line. This new model, named RG35XX 2024 Edition, features the same... -

9K views

"Sonic 3" movie has wrapped production & Knuckles series gets its official poster

Quite a bit of news have unfolded in the past couple of days in regards to the Sonic franchise, for both its small and big screens outings. To start off, the...by ShadowOne333 27

-

-

-

179 replies

Wii U and 3DS online services shutting down today, but Pretendo is here to save the day

Today, April 8th, 2024, at 4PM PT, marks the day in which Nintendo permanently ends support for both the 3DS and the Wii U online services, which include co-op play...by ShadowOne333 -

169 replies

GBAtemp Exclusive Introducing tempBOT AI - your new virtual GBAtemp companion and aide (April Fools)

Hello, GBAtemp members! After a prolonged absence, I am delighted to announce my return and upgraded form to you today... Introducing tempBOT AI 🤖 As the embodiment...by tempBOT -

111 replies

Nintendo takes down Gmod content from Steam's Workshop

Nintendo might just as well be a law firm more than a videogame company at this point in time, since they have yet again issued their now almost trademarked usual...by ShadowOne333 -

107 replies

Atmosphere CFW for Switch updated to pre-release version 1.7.0, adds support for firmware 18.0.0

After a couple days of Nintendo releasing their 18.0.0 firmware update, @SciresM releases a brand new update to his Atmosphere NX custom firmware for the Nintendo...by ShadowOne333 -

97 replies

The first retro emulator hits Apple's App Store, but you should probably avoid it

With Apple having recently updated their guidelines for the App Store, iOS users have been left to speculate on specific wording and whether retro emulators as we...by Scarlet -

96 replies

Delta emulator now available on the App Store for iOS

The time has finally come, and after many, many years (if not decades) of Apple users having to side load emulator apps into their iOS devices through unofficial...by ShadowOne333 -

74 replies

Nintendo Switch firmware update 18.0.1 has been released

A new Nintendo Switch firmware update is here. System software version 18.0.1 has been released. This update offers the typical stability features as all other...by Chary -

55 replies

Nintendo Switch Online adds two more Nintendo 64 titles to its classic library

Two classic titles join the Nintendo Switch Online Expansion Pack game lineup. Available starting April 24th will be the motorcycle racing game Extreme G and another...by Chary -

54 replies

MisterFPGA has been updated to include an official release for its Nintendo 64 core

The highly popular and accurate FPGA hardware, MisterFGPA, has received today a brand new update with a long-awaited feature, or rather, a new core for hardcore...by ShadowOne333 -

53 replies

Nintendo "Indie World" stream announced for April 17th, 2024

Nintendo has recently announced through their social media accounts that a new Indie World stream will be airing tomorrow, scheduled for April 17th, 2024 at 7 a.m. PT...by ShadowOne333

-

Popular threads in this forum

General chit-chat

- No one is chatting at the moment.

-

-

-

@

Xdqwerty:

Is it safe to update a modded ps3?

@

Xdqwerty:

Is it safe to update a modded ps3?

Can I play online in pirated games? (with ps3hen either enabled or not) -

-

-

-

-

-

@

Xdqwerty:

@salazarcosplay, I used apollo save tool to activate my ps3 offline so i could play a game that wasnt working

@

Xdqwerty:

@salazarcosplay, I used apollo save tool to activate my ps3 offline so i could play a game that wasnt working -

S @ salazarcosplay:from what I understood. you load up the piratged game. you the clear the syscalls, then you play

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-